## CHAPTER III

## HARDWARE DESCRIPTION OF THE KIT.

This chapter is intended to bring out essential features of the kit prototype, assumed while developing monitor software and the interpreter structure, which is suitable for cryophysics laboratories, as described in the previous chapter. Basic theme behind the development of hardware configuration has been to provide a complete form to the software developed, such that it could be tested through emulation on a PC/XT. As described earlier the environment of the microprocessor have already arown richer and it is always possible to select peripheral components, especially the memory modules, with a wide variety of options. present thesis is limited to accept a viable option than The entering into trade-off comparision of adopting alternative possibilities. Basic CPU configuration and memory mapping have been discussed in the first sub-section. I/O mapping and decode logic are covered in sec. 3.2, while the circuit option to intercouple the Ker prototype with a PC/XT are covered in the last sub-section.

## 3.1. The CPU Configuration And Memory.

The hardware provides two options for getting installed within environment of a PC/XT (or PC in general) viz. a ADD-ON kit or a multimaster (20) slave unit. Further, as outlined in Chapter I, the system is based on a CPU having 8086 as processing

unit. The 8086 has been configured in the maximum mode where the remaining components of configuration are 8284; the system clock generator, 8288; the system bus controller, 3 X 8282 s; octal latches, 2 X 8286 s; the bus transceivers, 8289; the bus arbitrar, is to be installed optionally. For both the options the maximum mode configuration is selected, allowing the same PCB getting converted to suit the requirements of the options. Details of circuit strappings have not been given a full stress at present. Configuration is shown in fig 2.3. This being an the standard configurations<sup>(26,34)</sup>, adoption of discussed throughly in the data sheets, wiring details and functional descriptions of various chips are not covered in the discussion. The fig. 3.1 does not include the bus arbitrar but the configurational details of option the PC ADD-ON are the multimaster slave are discussed in the following sections.

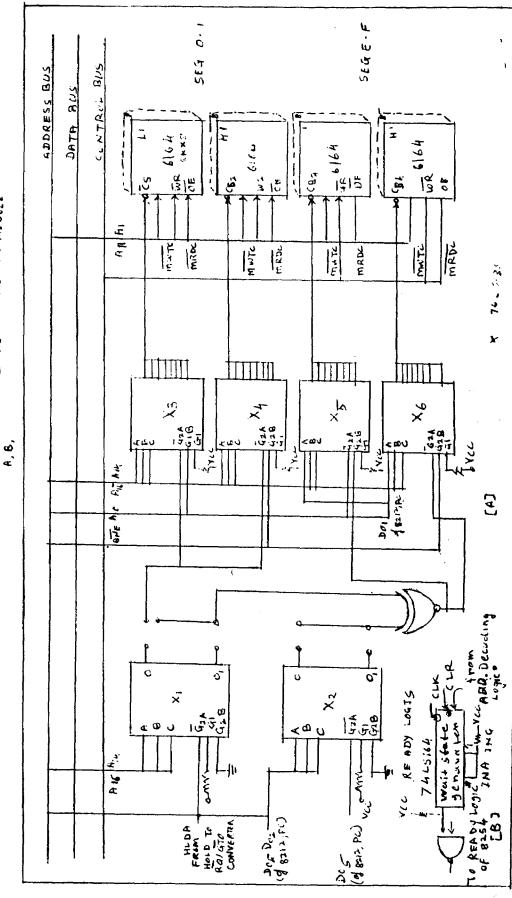

Regarding on-board memory facility, the system offers maximum of 256 KB of memory, where at present the equal weightage is given to the areas, viz. the program area and the object code area, i.e. upto 128 K max for each. The object code area includes the machine code routines defined by the user and the monitor, the interpreter deviced, while the program area stores the user written program and the data acquised. The present technology offers two options to configure the RAM memory use of static RAMs is recommended for low memory counts, while the higher density dynamic RAM units are prefered for larger memory requirements. Within the configurations 8086, 64 K X 1 dynamic RAM have been

commercially used<sup>(35)</sup>, and total number of 64 dynamic RAM chips would be required to satisfy the present memory requirement. As an alternative using 6164, a 8 K X 8, CMOS technology product, would demand the same chip count and is selected presently to configure the memory. This will definately be a faster choice, through detailed cost and reliability trade-offs are not estimated.

The decode logic is shown in fig. 3.1 (a). Out of the four segments the strapping option is provided to select the segments as 0 - 1, without option, and 2 - 3, ..., E - F by the kit CPU. When the CPU of PC takes charge of kit bus, the object code module area, i.e. segment 2 - 3, ..., E - F, will only be accessible and the decode logic is separate, allowing redefination of the segment. The decoders are switched either using a derived HLDA output or through a dedicated logic network (sec. 3.3). In PC ADD-ON option the object code memory module will be treated as a I/O device while in the multimaster slave configuration the object code memory module will be a dual port device (sec. 3.3.). The memory of the system as a whole is battery backed and monitor is assumed getting loaded from PC upon an interrupt from the kit, preferably NMI controlled through the keyboard. Further if needed part of the module could be replaced by 2764 units with too little a strapping required.

Logic distribution of memory is given in the table 3.1 and is self explanatory. Fig. 3.1 (b) shows a block diagram for

introduction of wait states. The basic unit of the block is a 8 bit shift register as required<sup>(34)</sup>. The same block applies with all the modules to generate on-board or off-board READY signals. This being too popular a option is not elaborated at present.

3.2. System I/O And Decode Logic.

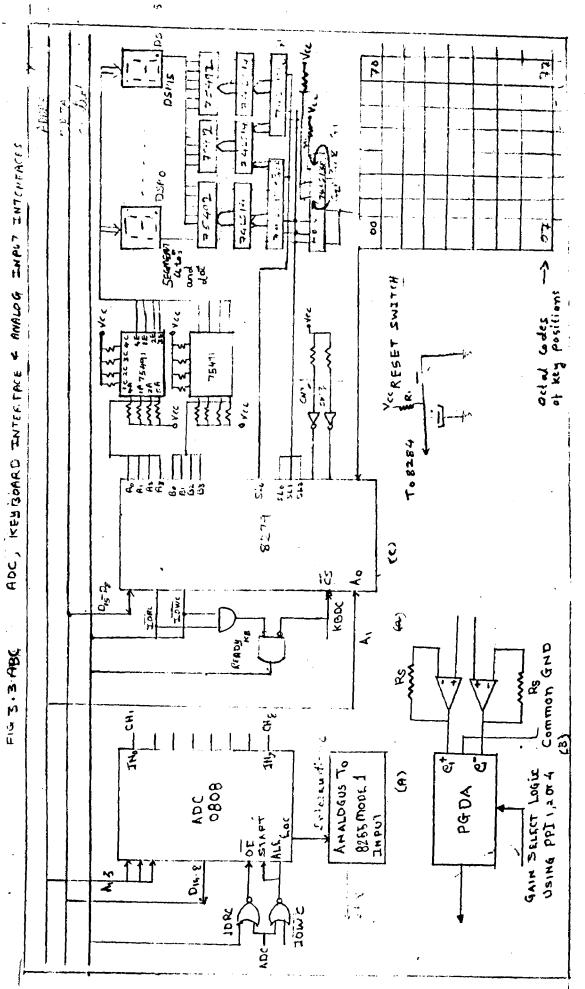

The I/O module shown in fig. 3.2 and fig. 3.3 comprises of decode logic, support peripherals including (2 + 2 optional) X 8255 (PPIs), 8279 (KeyBoard and Display Controller), 8251 (USART), 2 X 8254 (PITs), 8259 (PIC), 0808 (ADC), 2 X 8212 for the system use. The module is exclusively for the kit and a 2716 is used as a basic decoder. 8255s and 8279 is decoded directly, where configuration demanded a byte or a word transfer through PPIs. Additionally in combination with DO<sub>5</sub> - DO<sub>7</sub> of 2716 a 74LS138 is used to decode 7 more interface chips. The Table 3.3 shows the address map.

Ports of importance for the software development are discussed below :

1) 8212\_1 : It has been used to specify the total memory installed. The chip is in the input mode and informs status of a DIP switch connected to it. The information on the port is decoded in the following Table.

| agan kulo jaja alah kulo kulo k | DI3 | DIS | DI1 | DIO | ann dear dein laine ann ann dan aire ann ann dein fign doct ann ann ann ann ann ann ann |

|---------------------------------|-----|-----|-----|-----|-----------------------------------------------------------------------------------------|

|                                 | ×   | ×   | 0   | 0   | Not Allowed.                                                                            |

|                                 | ×   | ×   | 0   | 1   | 64 K.                                                                                   |

|                                 | ×   | ×   | 1   | 0   | 96 K,                                                                                   |

|                                 | ×   | ×   | 1   | 1   | 128 K.                                                                                  |

|                                 | 0   | 0   | ×   | ×   | Not Allowed.                                                                            |

|                                 | 0   | 1   | ×   | ×   | 2 PPIs                                                                                  |

|                                 | 1   | Ó   | x   | ×   | 3 PPIs                                                                                  |

|                                 | 1   | 1   | ×   | ×   | 4 PPIs                                                                                  |

|                                 |     |     |     |     |                                                                                         |

2) PPIs : The default mode setting of 8255s are as below :

PPI\_1 : MODE\_0 ; PORT\_A, \_B, \_C as INPUT\_PORT.

PPI\_2 : MODE\_C ; PORT\_A, \_B, \_C as OUTPUT\_PORT.

PPI\_3 (Optional) : MODE\_1; PORT\_A, \_CH, INPUT\_PORT, PORT\_B, \_CL

OUTPUT\_PORT.

PPI\_4 (Optional) : MODE\_0; PORT\_A, \_CH, INPUT\_PORT, PORT\_B, \_CL

OUTPUT\_PORT.

3) PIT\_1 : The default mode setting of 8254 is as below :

COUNTER\_1 : MODE\_3, with BCD counting and the counter loaded with 1000 as the count.

COUNTER\_2 : MCDE\_3, with BCD counting and the counter loaded with 0080 as the count.

System clock has been inputted to COUNTER\_1 (C\_1) while output of C\_1 is connected to CLK of C\_2 to generate a square wave of 1 KHz and is inputted to C\_0 in MODE\_0 to generate interrupt on the terminal count.

4) ADC : The address selection itself selfcts the channel. Further installation of PGDA<sup>(36)</sup>, LF356 buffers and additional demultiplexers to provide desired pre-amplification and high input impedance is possible. In this situation instead of ADC 0808, ADC 0800 will be employed. These interfaces are throughly discussed in DEM systems book<sup>(37)</sup>.

5) KeyBoard and Display Interface : This unit comprises 8279 as programmable controller. The device is selected to operate Hz and in 2 key roll over encoded scan mode. The display unit is in the left entry typewriter mode. Rest of the circuit configurations are too standard and the key codes corresponding to the various keys are given in Table 3.4.

Remaining features of I/O interfaces are transparent in the fig. 3.2 and fig. 3.3.

3.3. : Options For PC Interfacing.

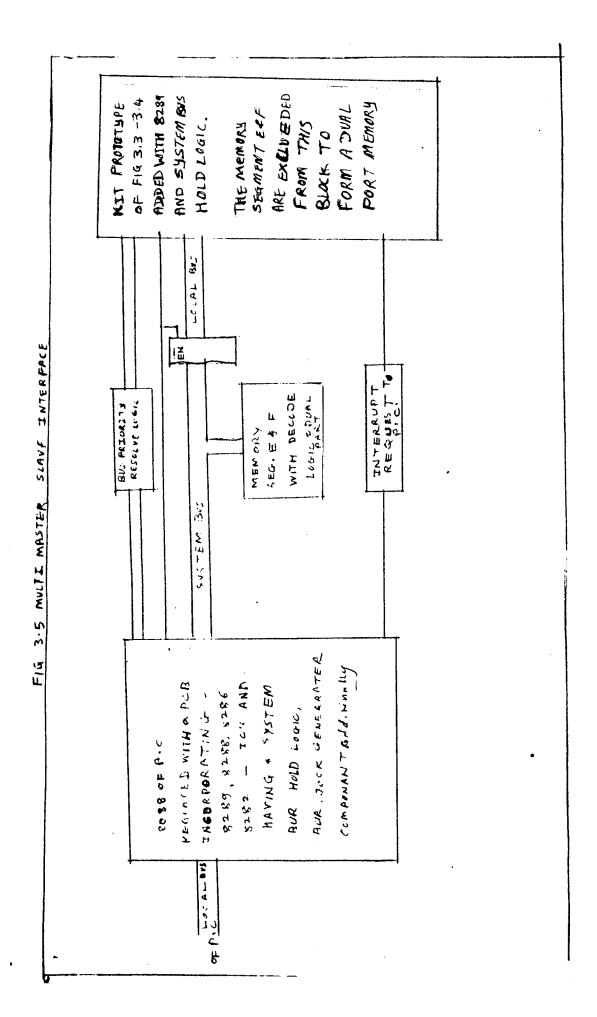

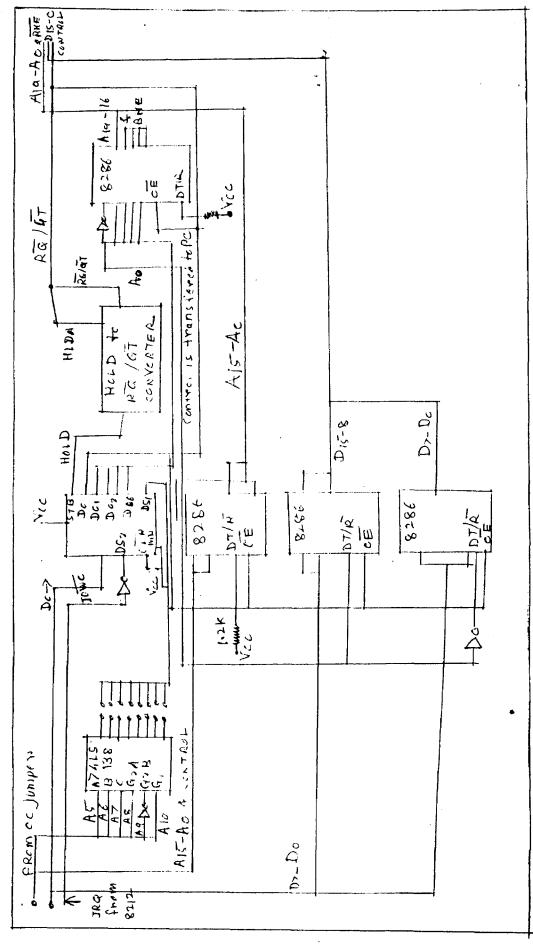

Fig. 3.4 and fig. 3.5 elaborates the PC ADD-ON interface and multimaster configuration respectively. The PC ADD-ON interface uses a 8212 in the control of PC to communicate HOLD signal and the segment addresses required. Further the same port provides enables to the buffers for address, data and control signals. The service is demanded via an interrupt request from the kit, through 8212\_2. A area in object code module of memory could be used for information and parameter transfer to the PC to decide the course of action to be executed. Using this information DMA

transfer will be executed by PC for the data transfer. Further elaboration on the .COM software needed to realise the interface is awaited.

Regarding the multimaster configuration at present we propose to replace 8088 of PC by a PCB, incorporating the multi bus termination. Further the board possesses a logic to acquire a system bus control and managing DMA transfers their\_next. The PC will be the master unit while the remaining kits will be the slaves. The bus arbitration logic leaves highest priority to the master. The inter-board communications is always through PC. The strategies adopted for selecting the parameters for data transfer at the level of PC ADD-ON option will be valid in this configuration also.

Table 3.1 : Logical Distribution of Memory.

|               | 0000<br>:<br>00FF         | INTERRUPT TABLE (64 INTERRUPT LEVELS)    |

|---------------|---------------------------|------------------------------------------|

|               | 0100<br>:<br>01FF         | DISPLAY ENTRY TABLE (256 BYTES).         |

|               | 0200<br>:<br>02FF         | DIT                                      |

|               | 0300<br>:<br>03FF         | PIT                                      |

|               | 0400<br>:<br>041F<br>0420 | CONVERT OFFSET TABLE (16 LEVELS).        |

|               | 045F<br>0460              | INTERMEDIATE PARAMETER TABLE             |

|               | :<br>047F<br>0480 <       | DATA REFERENCE TABLE.                    |

|               | 04DF  <br>:  >            | DATA ARRAY AREA (LRN MODE ONLY)          |

|               | 057F <'<br>0580<br>:      | KB BUFFER                                |

|               | 05AF<br>0580<br>:<br>061F | DISPLAY BUFFER                           |

|               | 0620<br>:<br>06FF         | USER STACK                               |

|               | 0700<br>:<br>0EFF         | RAM BUFFER                               |

|               | OFOO<br>:<br>OFFF         | OFFSET TABLE                             |

| ><br>!<br>!   | 1000<br>1                 | IC CODES                                 |

| ;<br>;<br>`-> | ¦<br>XXXX                 | DATA<br>DECIDED BY CONFIGURATION SWITCH. |

Table 3.2 : Logical Distribution of Memory. (Contd.)

0420 : LOCATIONS TO BE LOADED WITH FIXED VALUES : 042D 042E : LOCATIONS TO BE RESETTED AND VARIABLE PARAMETERS : GETTING LOADED AT THE EXECUTION TIME. 045F

The locations are specified in the listing enclosed.

Table 3.3 : I/O PORT ADDRESS MAP

| Hex Address                      | BHE              | I/O PORT                                               | Device        |

|----------------------------------|------------------|--------------------------------------------------------|---------------|

| FF80H<br>FF82H<br>FF84H<br>FF86H | 1<br>1<br>1      | PORT_A<br>PORT_B<br>PORT_C<br>PORT_CONTROL             | PPI_1,(8255)  |

| FF81H<br>FF83H<br>FF85H<br>FF87H | 0<br>0<br>0<br>0 | PORT_A<br>PORT_B<br>PORT_C<br>PORT_CONTROL             | PPI_2,(8255)  |

| FF80H<br>FF82H<br>FF84H<br>FF86H | 0<br>0<br>0<br>0 | PORT_A<br>PORT_B<br>PORT_C<br>PORT_CONTROL             | PPI_1 & PPI_2 |

| FF90H<br>FF92H<br>FF94H<br>FF96H | 1<br>1<br>1<br>1 | PORT_A<br>PORT_B<br>PORT_C<br>PORT_CONTROL             | PPI_3,(8255)  |

| FF91H<br>FF93H<br>FF95H<br>FF97H | 0<br>0<br>0<br>0 | PORT_A<br>PORT_B<br>PORT_C<br>PORT_CONTROL             | PPI_4,(8255)  |

| FFAOH                            | 1                | R/W KBDC DISPLAY<br>RAM OR READ KBDC                   | KBDC (8279)   |

| FFA2H                            | 1                | FIFO.<br>READ KBDC STATUS<br>OR WRITE 8279<br>COMMAND. |               |

| Hex Address                      | BHE              | I/O PORT                                                 | Device                                                                                   |

|----------------------------------|------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|

| FFB1H<br>FFB3H<br>FFB5H<br>FFB7H | 0<br>0<br>0<br>0 | COUNTER_O<br>COUNTER_1<br>COUNTER_2<br>CONTROL_REG       | PIT_1 (8254)                                                                             |

| FFBOH<br>FFB2H<br>FFB4H<br>FFB6H | 1<br>1<br>1<br>1 | COUNTER_O<br>COUNTER_1<br>COUNTER_2<br>CONTROL_REG       | PIT_2 (8254)                                                                             |

| FFC1H                            | 0                | DATA_PORT                                                | 8212_1                                                                                   |

| FFCOH<br>FFC2H                   | 1<br>1           | CONTROL_WORD                                             | PIC (8259)                                                                               |

| FFD1H<br>FFD3H                   | 0<br>0           | R/W DATA_PORT<br>READ 8251 STATUS,<br>WRITE 8251 CONTROL | USART(8251)                                                                              |

| FFDOH<br>FFD2H                   | 1                | ADC CH_O<br>ADC CH_1                                     | ADC 0808                                                                                 |

| FFDEH                            | 1                | ADC CH_7                                                 | and and the state and state and and and and and the time and the state and a solar bails |

| FFE1H                            | 0                | DATA_PORT                                                | 8212_2                                                                                   |

:

| KEY MNEMONIC | HEX CODE | KEY MNEMONIC<br>(FUNCTION) | HEX CODE   |

|--------------|----------|----------------------------|------------|

| 0            | 00       | СН                         | 30         |

| 1            | 01       | CNVRT                      | 40         |

| ż            | * 02     | RET                        | 44         |

| 3            | 03       | DLY                        | 48         |

| 4            | 04 .     | OUB                        | 4C         |

| 5            | 05       | INB                        | 50         |

| 6            | 06       | INW                        | 54         |

| 7            | 07       | INR                        | 58         |

| 8            | 08       | OUW                        | 5C         |

| 9            | 09       | LET                        | 60         |

| A            | 0A       | DCR                        | 64         |

| В            | OB       | IF                         | 68         |

| С            | oc       | GSB                        | 6C         |

| D            | OD       | DSP                        | 70         |

| E            | OE       | FOR                        | 74         |

| F            | OF       | GTO                        | 78         |

| •            | 10       | NXT                        | 7C         |

| \$           | 2B       | END                        | 81         |

| ,            | 20       | THEN                       | 82         |

| ENTER        | 2D       | AUTO                       | 85         |

|              | 2E       | LRN                        | 87         |

| ÷            | 2F       | DAT                        | 8D         |

| ¥            | 30       | RUN                        | 91         |

| 1            | 31       | LST                        | 95         |

|              | 32       | VAC                        | 99         |

| ≠            | 33       | DEL                        | A1         |

| <            | 34       | EXT                        | A5         |

| < ==         | 35       | NOR                        | A9         |

| >            | 36       | 16I                        | AD         |

| >=           | 37       | 24R                        | B1         |

| КВ           | 38       | allian attain              | ators data |

Table 3.4 : Key Codes Of The Keys Used.

•

ĩ

. .

,

| KEY MNEMONIC<br>(REAL VARIABLE                                               |                                                                                                          | : KEY MNEMONIC<br>: (INTEGER VARI              |                                                          |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J<br>K<br>L<br>M<br>N<br>O<br>P | 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>23<br>24<br>25<br>26 | Q<br>R<br>S<br>T<br>U<br>V<br>W<br>X<br>Y<br>Z | 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 |

| KEY MNEMONIC<br>(CURSOR)                                                     | HEX CODE                                                                                                 |                                                | ann dan fan ann ann ann ann ann ann ann ann a            |

| ><br><<br>I<br>i                                                             | 3A<br>3B<br>3D<br>3E                                                                                     |                                                |                                                          |

FIG 2.1 DECODE TOUT UND WEWBER WEDTE

,

LCT KE-STATIS 45.24 1515 . H. 36 C ADC OLO CASSATL TAPE RECORDIA CONTRALS 1 500 F ERRER DETALT DOL AX ANI 20 6363 53 33 <del>ار</del> ۲<sub>رد</sub> CONTROL ADDRE SS 3 DATA 50 ALNI ALNI DIS-Dg 10-76 TO BE USED WITH FSK MODEN MC 44413 4 IN 324 MMC 606 CASATE TAPE RECORDED 510 SYN DC C Puie () \* (-) (-) ど介 5528 (4) E BERNE Dis-De 18 19,3 T D -E99 Slake 10 PB Hand Cate TO BE CONFIGURES FOR ARTIFICIAL VOILEE GENERATION GMer Dy.0 E A CLK3 GATE CUT2 CLX0 8254 -2-୧2 ୫ନି (3) CS ho-jop 19/5 Dy-Dg D9-0 F-Idd 1 A2 Timer ÷

FIG 3.2 6 T/0 DECODE AND PERIPHENALS

FL4 3.4 PC PUB-ON INTERFACE